컴퓨터 구조 - 기본적인 논리회로 - 조합회로 및 순차회로

기본적인 조합회로 및 순차회로

이전에 포스팅했던 논리 게이트들을 조합하여 여러 회로를 만들 수 있다.

수를 더하는 회로부터 두 값을 비교하는 회로등 이런 회로들이 모여 컴퓨터를 이룬다. 이번 포스팅에서는 컴퓨터를 구성하는데 필요한 기본적인 논리회로에 대해 알아보겠다.

1. 조합 회로

입력값만 결과값에 영향을 미치는 회로이다.

1) Half-adder(반가산기), Full-adder(전가산기)

값을 더하는 회로이다. 가산기당 1bit를 연산할수있으므로 n비트의 연산이 필요하다면 n개의 가산기를 병렬로 연결한뒤 하위 carry_out을 상위 carry_in에 연결하면 된다.

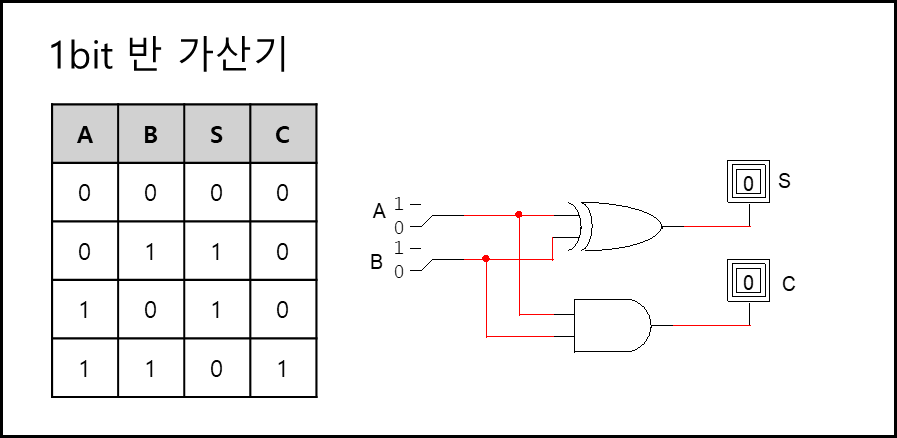

a. Half-adder(반가산기)

이전에 올라오는 올림수(Carry)를 고려하지 않는 회로이다.

※ 수식

$S = \overline{A}B + A\overline{B} = A\oplus B$

$C = A\cdot B$

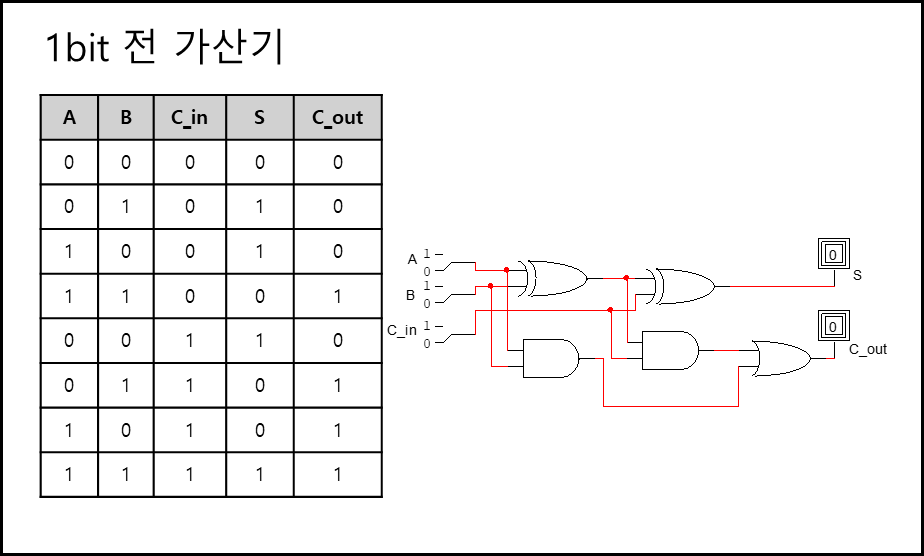

b. Full-adder(전가산기)

이전에 올라오는 올림수(Carry)를 고려하는 회로이다.

※ 수식

$S = A\oplus B \oplus C$

C_out = C_in$(A \oplus B) + AB$

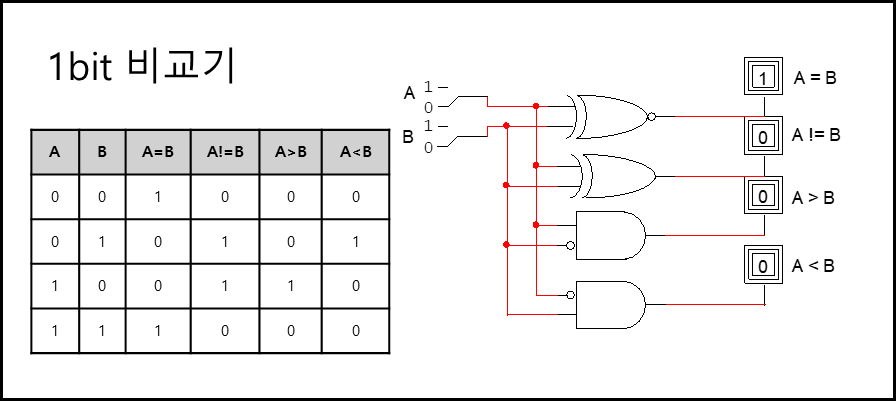

2) Comparator(비교기)

입력되는 두 값이 같은지, 다른지, 큰지, 작은지를 비교하는 회로이다. 아래의 회로는 1bit 비교기이다. 두 1비트 값이 같은지 다른지 큰지 작은지를 체크한다.

※ 수식

A=B : $\overline{A\oplus B}$

A!=B : $A \oplus B$

A>B : $A\overline{B}$

A<B : $\overline{A}B$

3) Encoder, Decoder

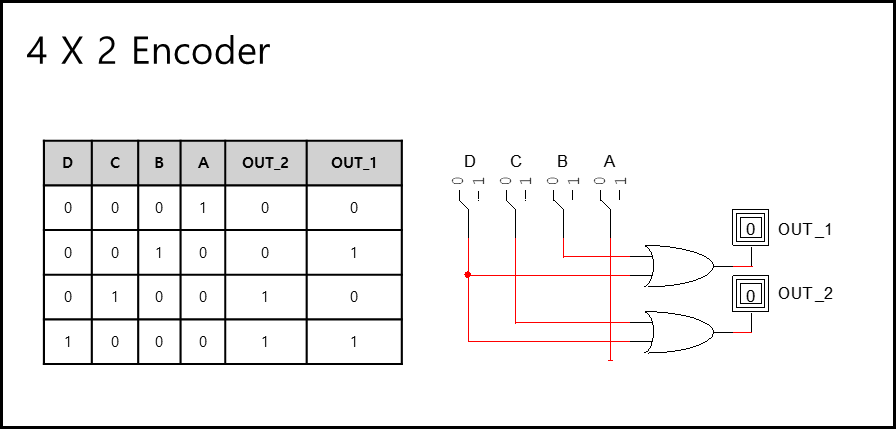

a. Encoder

개수가 많은 입력을 개수가 적은 출력으로 변환해서 출력하는 회로이다.

각각의 신호에 대해서 동시 입력에 대해서는 고려하지 않으며

다수의 입력 중 하나의 입력만 들어왔을때의 경우에 이미 예정된 값으로 출력해준다. 아래는 4개의 신호 중 하나를 output 신호 2개로 표현했을때의 회로이다.

※ 수식

OUT_1 : $B+D$

OUT_2 : $C+D$

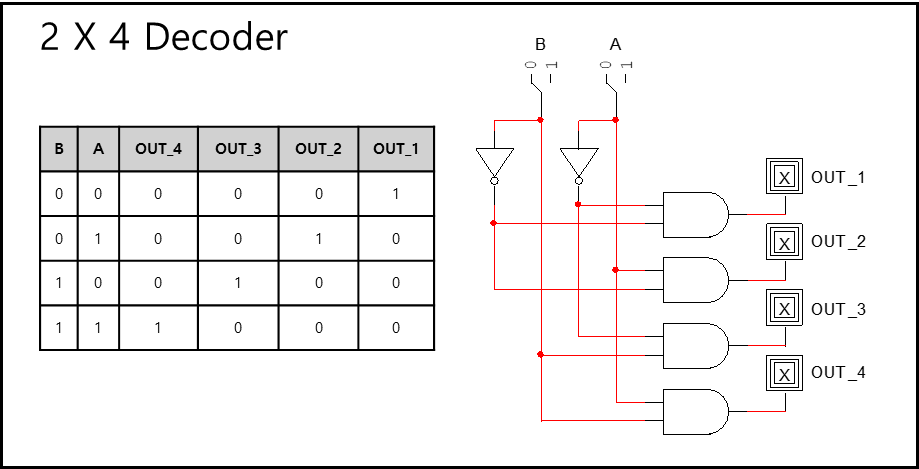

b. Decoder

개수가 적은 입력을 개수가 많은 출력으로 변환해서 출력하는 회로이다.

입력값에 따라 각 출력 대상 중 하나에만 출력을 전달시킨다.

출력 대상 중에 두 개 이상이 출력되는 경우는 고려하지 않는다.

아래의 회로는 2개의 신호를 4개 중 한 개의 신호로 변환해서 출력하는 회로이다.

※ 수식

OUTPUT_1 : $\overline{B}\overline{A}$

OUTPUT_2 : $\overline{B}A$

OUTPUT_3 : $B\overline{A}$

OUTPUT_4 : $BA$

4) Multiplexer, Demultiplexer

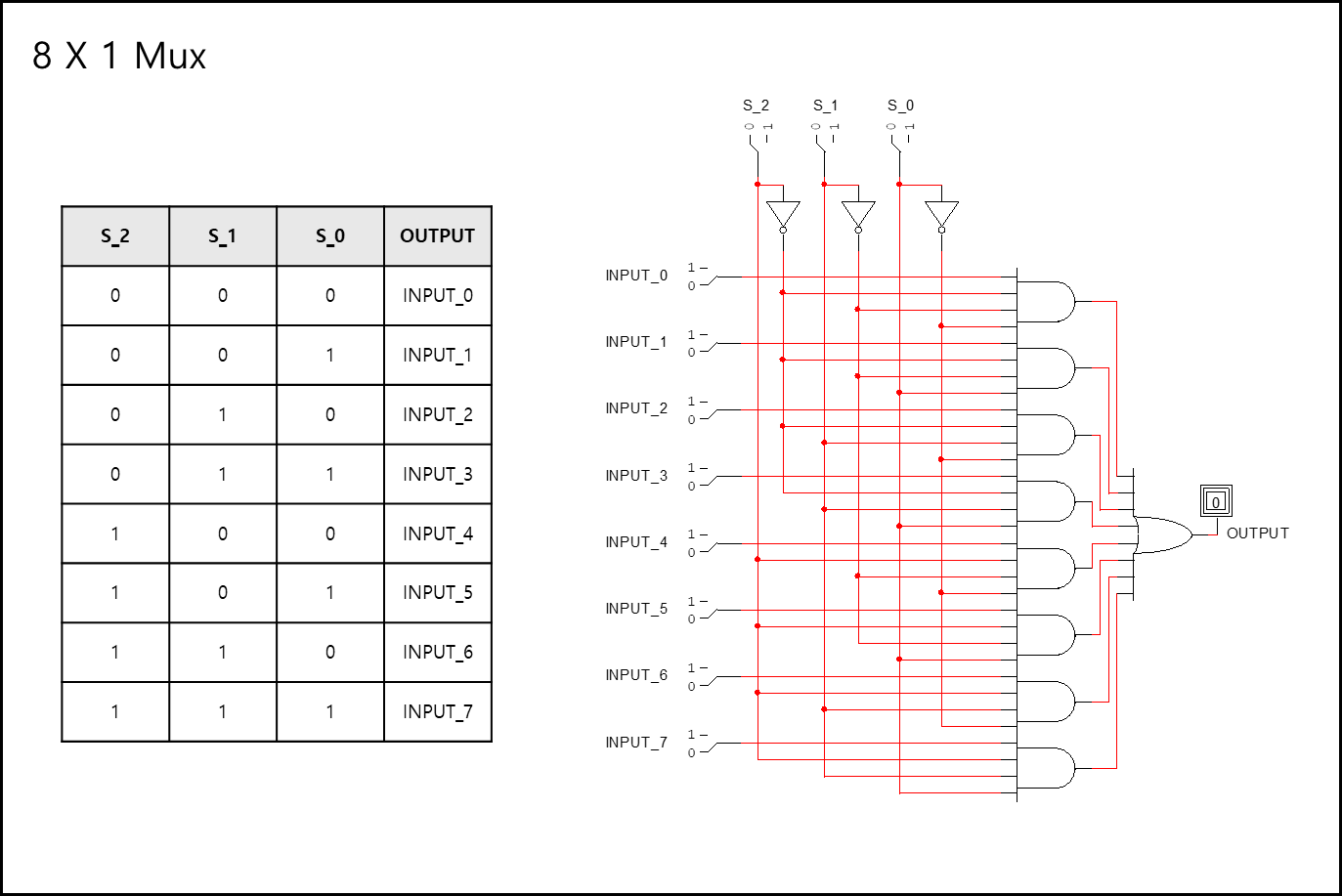

a. Multiplexer

Mux라고도 부른다. 여러 입력 중 하나를 선택하여 출력하는 회로이다.

입력이 여러개 있으며 Selector의 값에 따라 어떤 입력값을 출력할지 결정된다.

아래의 회로는 8개의 입력이 Selector의 값에 따라 어떤것 하나만 출력할지 결정할 수 있는 mux이다.

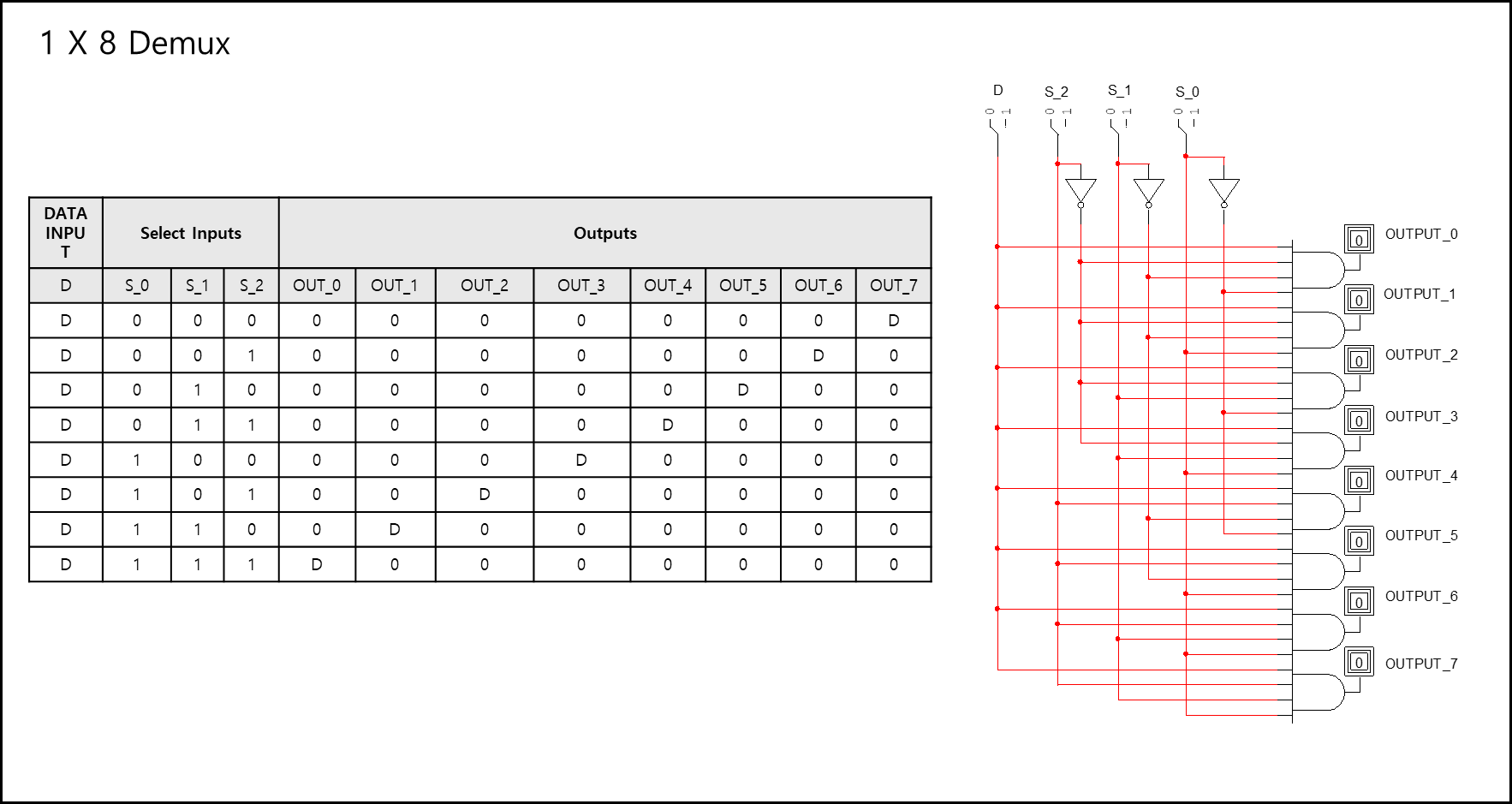

b. Demultiplexer

Demux라고도 부른다. 하나의 입력을 여러 곳 중 하나에 선택하여 출력하는 회로이다.

mux와는 반대로 Selector의 값에 따라 어느 곳으로 입력값이 출력될지 결정된다.

2. 순서 회로(Sequential Circuit)

순서 논리회로, 순차회로, 순차 논리회로 다 같은 말이다.

입력값과 이전 상태가 결과값에 영향을 미치는 회로이다.

이전 데이터를 저장하고 있다는 뜻이기 때문에 메모리로 쓰이기 적합한데 용량이 커질수록 1비트당 단가가 올라가므로 주로 소용량의 메모리인 레지스터나 CPU 캐시에 쓰인다.

(RAM과 같은 장치의 구조는 다음에 기회가 있을때 언급하겠다)

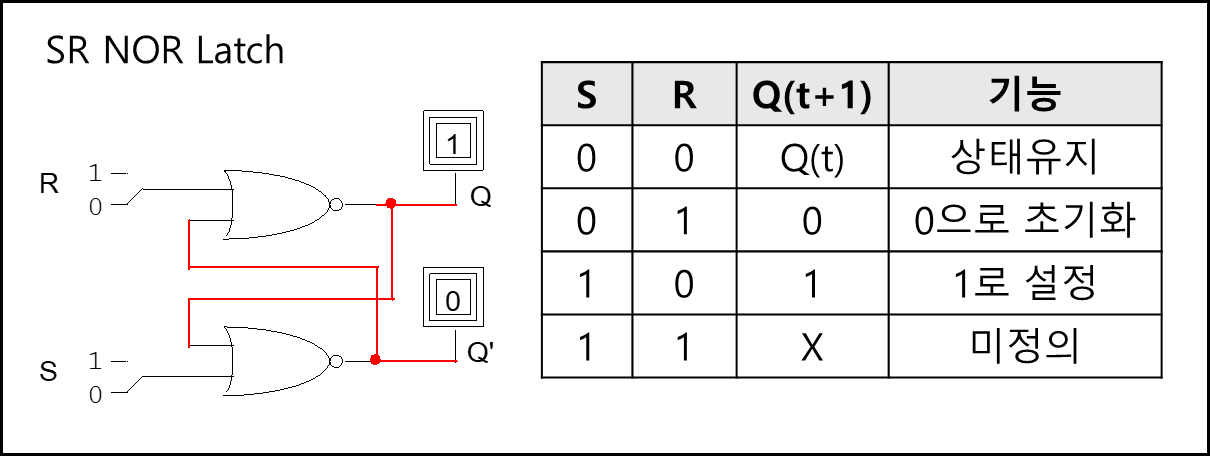

1) 래치(Latch)

입력값이 들어가자마자 결과값이 나오는 회로이다. 입력을 반영할지 말지 결정할 수 있는 Gate가 달린 Latch와 Gate가 달리지 않은 Latch로 구분 할 수 있다. Gate가 달린 Latch는 Gate 입력 값이 High일때만 입력 값이 반영된다.

a. SR NOR Latch

가장 간단한 순차회로이다. 여기서 S는 set, R은 reset을 뜻하는 것으로 S는 출력을 1로, R은 출력을 0으로 되도록 한다는 뜻이다. 현재 저장된 상태 출력은 Q로 표시하며 여기서는 S와 R 둘다 1인 경우는 사용하지 않는다.

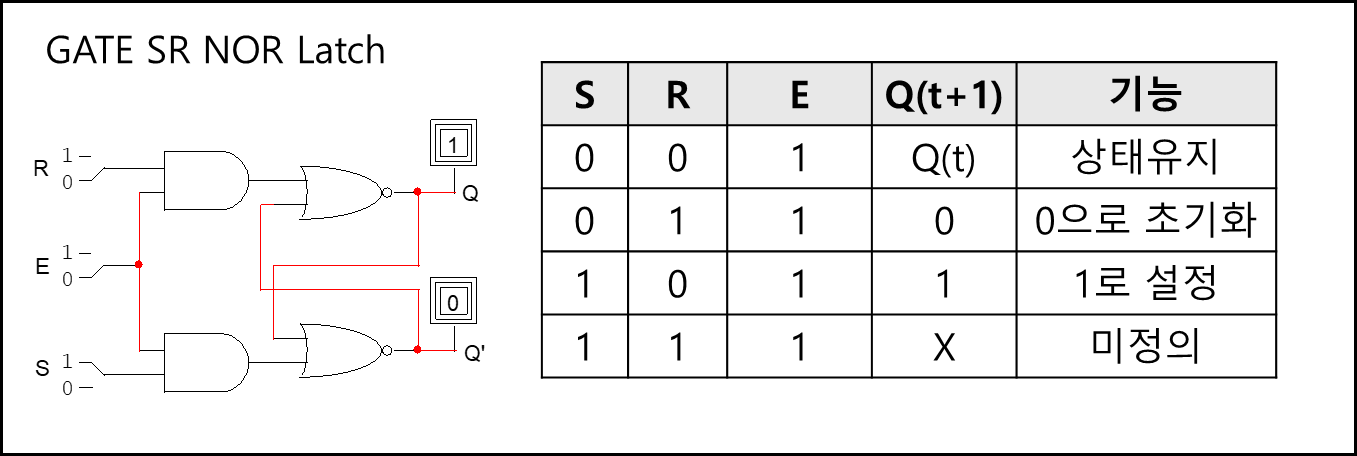

b. GATE SR NOR Latch

Gate가 high일때만 Latch 입력값이 출력값에 반영되는 Latch이다.

Gate가 high일때만 작동한다는 점만 제외하면 나머지는 동일하다.

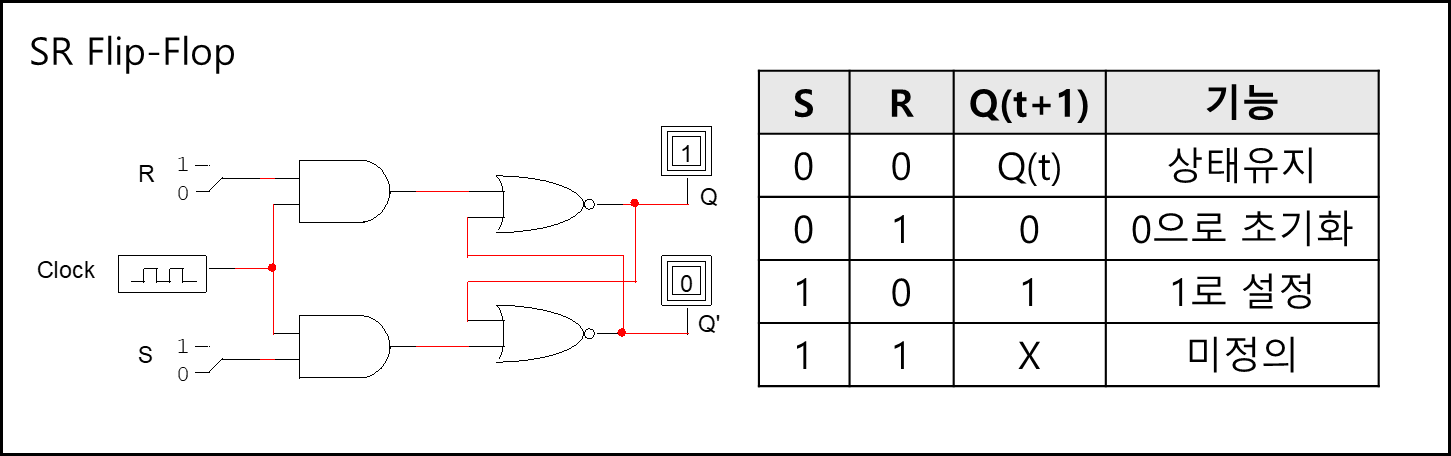

2) 플립플롭(Flip-Flop)

클럭에 맞춰 결과값이 나오는 회로이다. 클럭을 입력 받을 수 있는 래치를 사용하는데 클럭이 low에서 high로 이동할때만(Edge Trigger) 입력이 반영되고 아니면 무시된다.

(단, 입력을 반영할건지 말건지 gate가 달려있는 래치와는 다르다. gate 래치는 gate값이 Edge Trigger일때만 아니라 high일때 내내 입력이 반영된다)

※ 클럭(Clock)

일정 주기로 0과 1을 반복하는 것이다. 1초에 0과 1이 한번 반복될때 1Hz라고 하는데 이 주기가 짧을 수록 Hz는 높아지고 초당 처리할 수 있는 연산 횟수가 늘어난다. 동기식 플립플롭을 쓰는 이유는 회로가 복잡해질 경우 결과 나오는 주기를 맞추기(동기화)에 용이하기 때문이다.

a. Synchronous SR NOR Flip-Flop

기존 SR NOR Latch에서 clock을 받는 회로만 추가되었다.

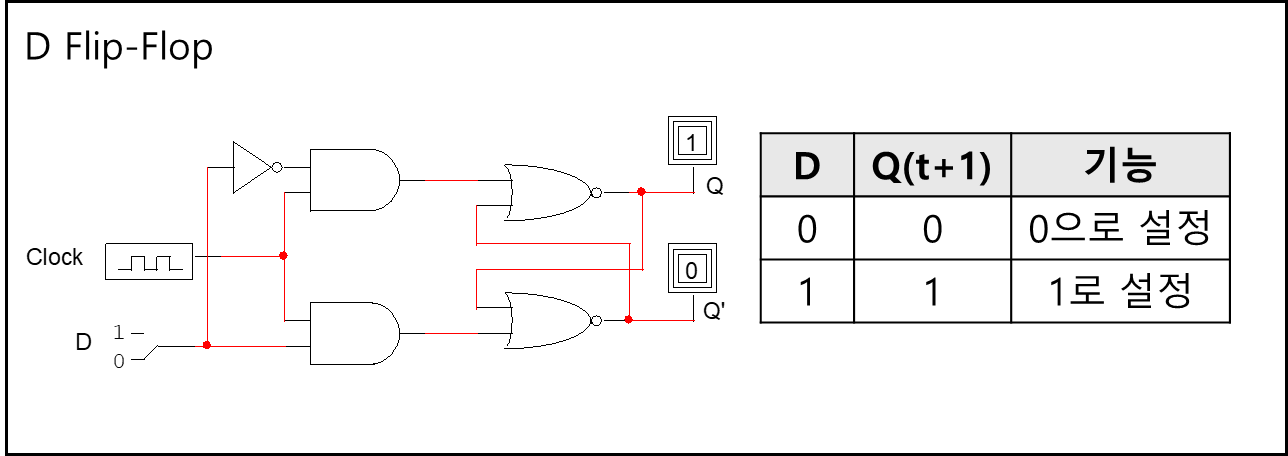

b. D Flip-Flop

여기서 D는 Delay의 약자로 주로 버퍼용으로 많이 사용한다.

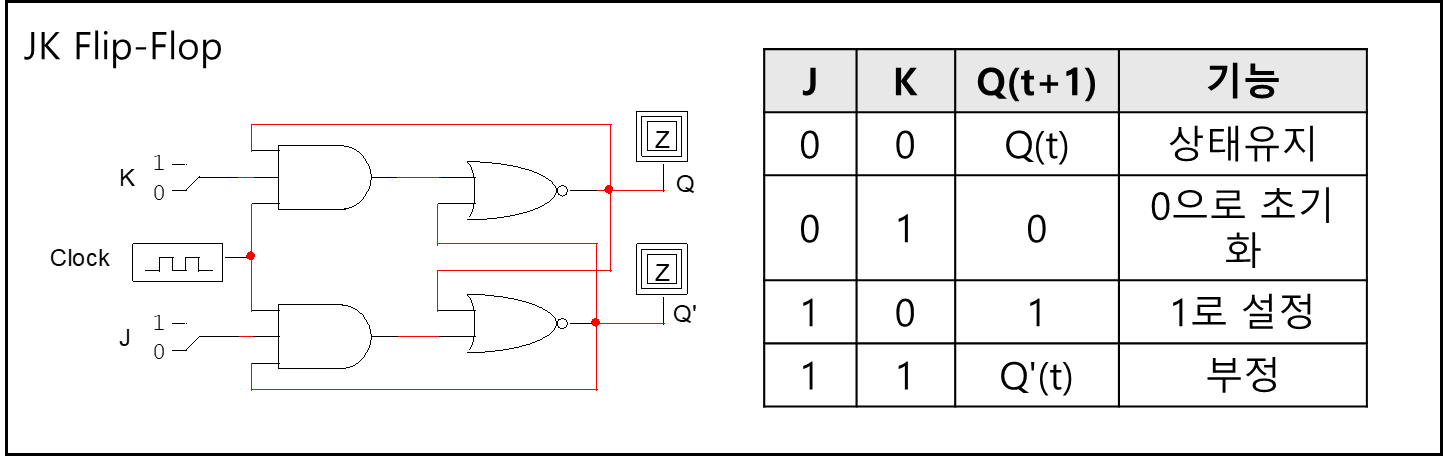

c. JK Flip-Flop

RS 래치에서 RS가 11일때 사용하지 않는 것을 토글로 바꾸어 동작하도록 만들어진 플립플롭으로 RS 플립플롭에서 토글기능을 합친 플립플롭니다.

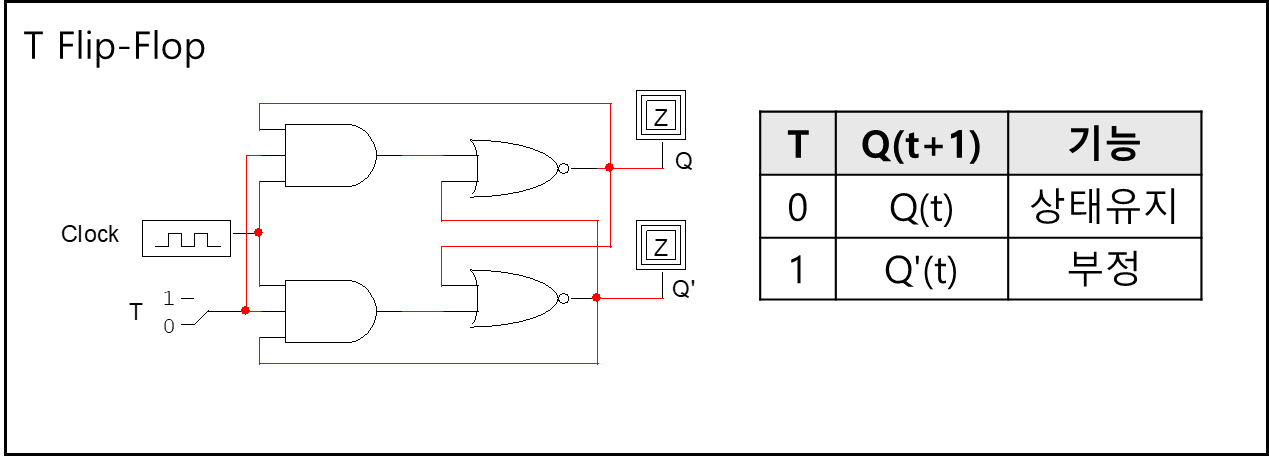

d. T Flip-Flop

여기서 T는 Toggle의 약자이다.

입력 T가 High이면 Q의 출력이 반대로 전이된다.

참고자료

- Contemporary Logic Design(2004, written by Randy H. Katz, Gaetano Borriello)

- 일상을 기록하며 되돌아보기 - 조합회로와 순차회로

- Different Types of Demultiplexers

- Matricaria - [Chapter1 조합논리회로] 02. 비교기

- 호무비의 IT 지식 창고 - [컴퓨터 구성] #9 플립플롭(Filp-Flop)과 그 종류 (SR, D, JK, T)

- 위키백과 - 플립플롭