컴퓨터 구조 - CPU 구조 - 레지스터

Register

산술적/논리적 연산이나 정보 해석, 전송 등을 할 수 있는 일정 길이의 정보를 저장하는 중앙 처리 장치(CPU) 내의 기억 장치. 저장 용량에는 제한되어 있으나 주기억 장치에 비해서 접근 시간이 빠르고, 체계적인 특징이 있다. 컴퓨터에는 산술 및 논리 연산의 결과를 임시로 기억하는 누산기(accumulator), 기억 주소나 장치의 주소를 기억하는 주소 레지스터(address register)를 비롯하여 컴퓨터의 동작을 관리하는 각종 레지스터가 사용된다.

1. 구조

1) 기본 데이터 입출력

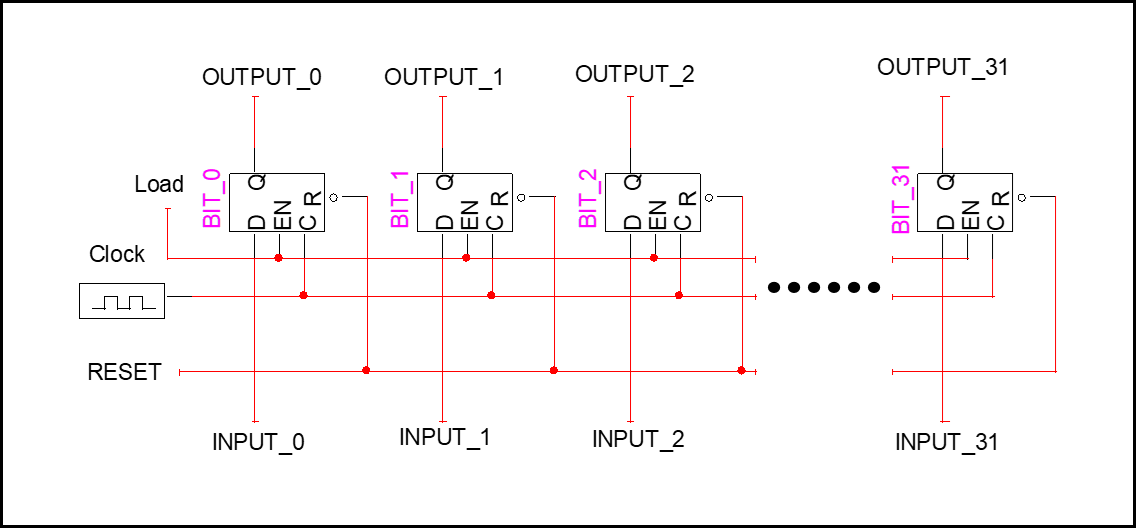

데이터를 보관해야하기 때문에 상태를 저장할 수 있는 플립플롭을 연결해서 구현한다.

가장 일반적으로 사용되는 플립플롭은 D 플립플롭인데, 동기화를 맞추기 위해서 Enable Gate가 달린 D 플립플롭을 사용하며 아래와 같은 구조를 둔다.

위의 회로는 D 플립플롭을 32개 연결하여 32bit 데이터를 한번에 저장하고 불러올 수 있게 만들어진 회로이다.

LOAD값이 0이면 D플립플롭에 입력값이 반환이 안되니 데이터가 그대로 유지되고, LOAD값이 1이면 입력값이 반환되는 식이다.

2) 특수 용도

일반적으로 데이터를 입출력하는 것만이 아닌 특수 용도로 제작된 Register가 있다.

이런 것들은 단순 D 플립플롭을 연결한 것만 아니라 추가적인 회로 구성해서 달거나 다른 회로로 레지스터를 구성한 경우이다.

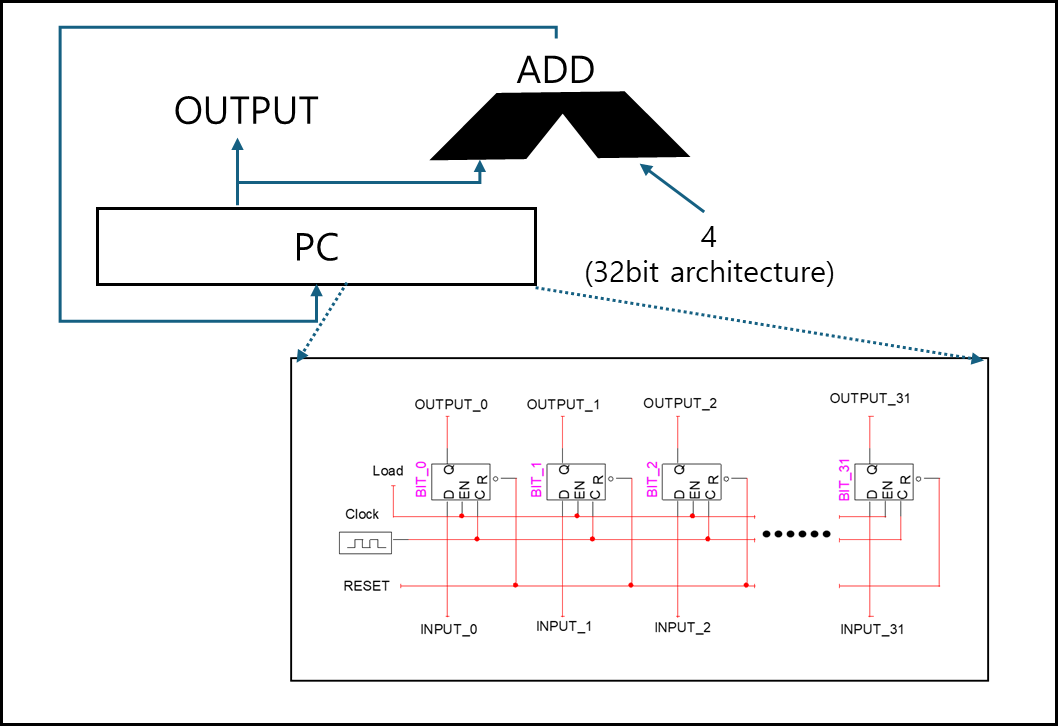

a. PC(Program Counter)

그 다음 실행할 주소를 담아두는 레지스터이다.

클럭에 따라 레지스터의 값이 주소 단위만큼 증가하는 특성을 가지고 있다.

이런 PC의 경우 기본적인 레지스터에 주소 단위만큼 증가하는 회로를 달아서

증가된 OUTPUT 값을 PC에 INPUT 값으로 넣는다.

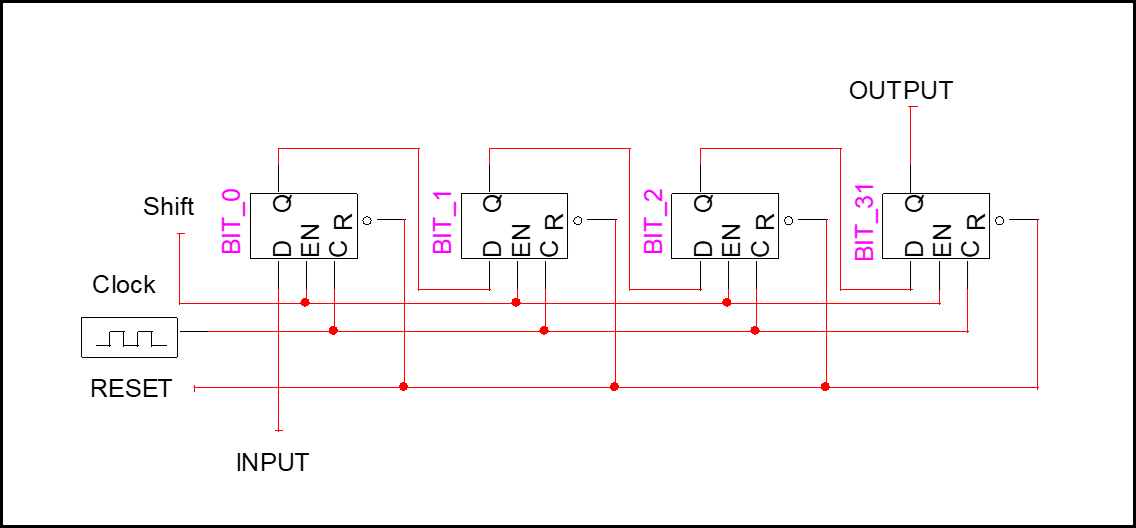

b. Shift Register

이진 단위로 1bit씩 shift하는 연산의 경우 아예 회로로 구현하면 빠르고 좋다.

때문에 shift Register라는게 있는데, 기본적으로 레지스터에 shift 연산이 추가된 형태이다.

직렬 쉬프트 레지스터

아래의 그림은 4bit 짜리 직렬 쉬프트 레지스터로 한번 클럭 주기마다 데이터가 1bit 씩 쉬프트 된다.

입력이 1bit 받을 수 있고 출력 역시 1bit씩 일어난다.병렬 쉬프트 레지스터

아래 그림은 4bit 짜리 병렬 쉬프트 레지스터로 한번 클럭주기마다 데이터가 1bit씩 쉬프트 된다. 직렬 쉬프트 레지스터와는 다르게 병렬 입력, 병렬 출력을 지원하므로 데이터가 동시에 로드되고 동시에 출력이 된다.

shift 신호가 1이면 기본적으로 1bit씩 쉬프트되며 shift가 0, load가 1이면 레지스터에 데이터가 입력된다.